# INTEGRATED CIRCUITS

CMOS ICs for Clocks, Watches and Real Time Clocks

Data Handbook IC16 1998

PHILIPS

**PHILIPS**

Let's make things better.

# **QUALITY ASSURED**

Our quality system focuses on the continuing high quality of our components and the best possible service for our customers. We have a three-sided quality strategy: we apply a system of total quality control and assurance; we operate customer-oriented dynamic improvement programmes; and we promote a partnering relationship with our customers and suppliers.

# **PRODUCT SAFETY**

In striving for state-of-the-art perfection, we continuously improve components and processes with respect to environmental demands. Our components offer no hazard to the environment in normal use when operated or stored within the limits specified in the data sheet.

Some components unavoidably contain substances that, if exposed by accident or misuse, are potentially hazardous to health. Users of these components are informed of the danger by warning notices in the data sheets supporting the components. Where necessary the warning notices also indicate safety precautions to be taken and disposal instructions to be followed. Obviously users of these components, in general the set-making industry, assume responsibility towards the consumer with respect to safety matters and environmental demands.

All used or obsolete components should be disposed of according to the regulations applying at the disposal location. Depending on the location, electronic components are considered to be 'chemical', 'special' or sometimes 'industrial' waste. Disposal as domestic waste is usually not permitted.

# CMOS Integrated Circuits for Clocks, Watches and Real Time Clocks

|                              |             | CONTENTS |

|------------------------------|-------------|----------|

|                              |             | Page     |

| INTRODUCTION                 |             | 3        |

| INDEX                        |             | 5        |

| SELECTION GUIDES             | •           | 9        |

| GENERAL                      |             | 19       |

| DEVICE DATA (in alphanumeric | c sequence) | 27       |

| PACKAGE INFORMATION          |             | 217      |

| DATA HANDROOK SYSTEM         |             | 229      |

#### **DEFINITIONS**

| Data sheet status         |                                                                                                                                                                                |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | This data sheet contains target or goal specifications for product development.                                                                                                |

| Preliminary specification | This data sheet contains preliminary data; supplementary data may be published later.                                                                                          |

| Product specification     | This data sheet contains final product specifications.                                                                                                                         |

| Short-form specification  | The data in this specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook. |

# **Limiting values**

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

# **Application information**

Where application information is given, it is advisory and does not form part of the specification.

# LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

# **PURCHASE OF PHILIPS I<sup>2</sup>C COMPONENTS**

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specification defined by Philips. This specification can be ordered using the code 9398 393 40011.

# CMOS integrated circuits for clocks and watches

# Introduction

Dear Customer,

Philips Semiconductors is one of the most important producers of CMOS integrated circuits for clocks and watches in the world. Situated in Switzerland, the heart of the European clock and watch industry, Philips Semiconductors benefits to a large degree from this unique industrial environment. It is therefore not surprising, that Philips was one of the first semiconductor companies to apply the silicon gate CMOS (complementary metal oxide semiconductor) technology in the production of clock and watch circuits and was the first company to offer an SO package (mini-pack) back in the seventies.

Philips Semiconductors maintains its position at the forefront of the clock and watch IC industry, being the first company to offer the EEPROMs (electrically erasable programmable read only memories), with operating voltages as low as 1.1 v, for time adjustment. This latest development enables the industry to find better technical and cost effective solutions for their products.

To enable the clock and watch industry to maintain its word-renowned quality image, Philps Semiconductors has implemented a Company-Wide Total Quality Management (TQM) program. This TQM program, involving every employee, features a continuous improvement of customer service and product quality. This commitment to quality has lead to us being able to set our standard at zero defect and now enables us to offer our customers a zero defects warranty. The warranty means that if he finds a single device which does not conform to the published specification, the customer can return the complete lot for rescreening or replacement. Faselec is the first company in the world to offer the clock and watch industry a zero defects warranty.

At PhilipsSemiconductors quality dominates all phases of manufacture. Quality is built into the product by the conscious use of advanced technological aids and a continuous monitoring off process steps (SPC) through in-line quality controls. Additionally a stringent incoming inspection of all materials used assures an end-product with an inherently high quality level.

All products are 100% tested against published specifications, any device not conforming to the specifications is rejected. Conformity of each lot to the published specifications is double-checked by our Quality department, which is independent from production.

The dedication of the high-qualified personnel and the large amount of know-how accumulated over the years, backed by constant efforts in developing new process and packaging technology as well as new products, makes Philips Semiconductors the preferred source for your clock and watch circuits.

# **INDEX**

# CMOS integrated circuits for clocks and watches

Index

| Type number    | Description                                                        | Page |

|----------------|--------------------------------------------------------------------|------|

| PCA146Xseries  | 32 kHz watch circuit with adaptive motor pulse                     | 28   |

| PCA148X series | 32 kHz watch circuit with adaptive motor pulse                     | 45   |

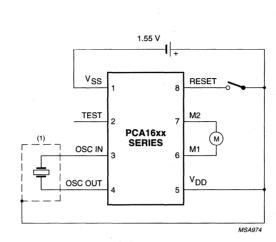

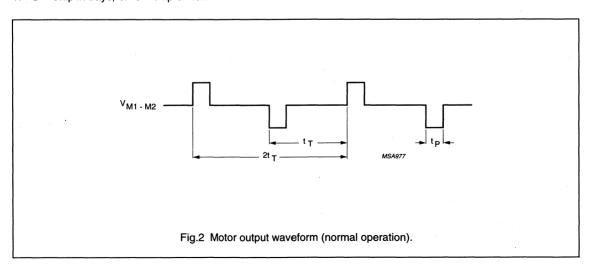

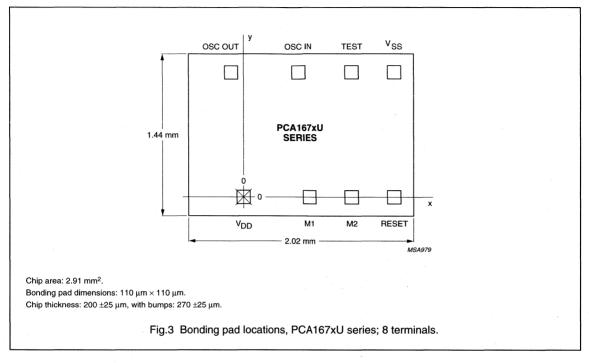

| PCA16XXseries  | 32 kHz watch circuit with EEProM                                   | 60   |

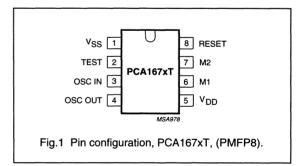

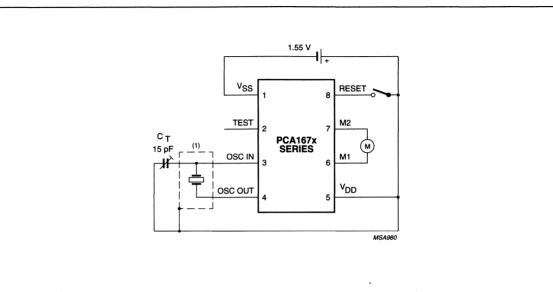

| PCA167Xseries  | 32 kHz watch circuit using a silver-oxide or a 3 V lithium battery | 69   |

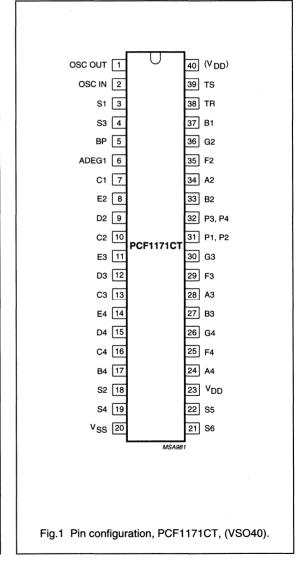

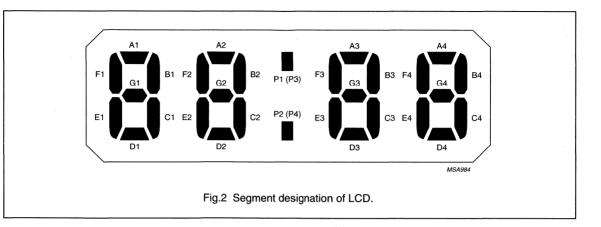

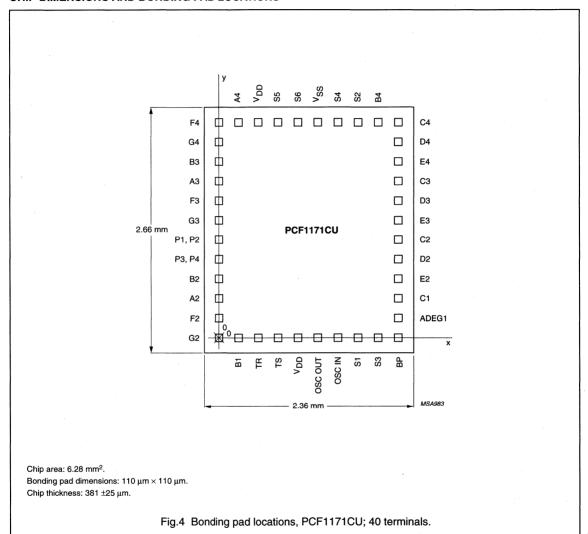

| PCF1171C       | 4-digit LCD car clock                                              | 75   |

| PCF1172C       | 3 1/2-digit LCD car clock                                          | 83   |

| PCF1174C       | 4-digit static LCD car clock                                       | 91   |

| PCF1175C       | 4-digit duplex LCD car clock                                       | 103  |

| PCF1178C       | 4-digit duplex LCD car clock                                       | 115  |

| PCF1179C       | 4-digit duplex LCD car clock                                       | 127  |

| PCF8563        | Real time clock/calendar                                           | 139  |

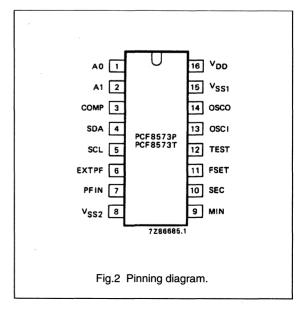

| PCF8573        | Clock/calendar with power fail detector                            | 157  |

| PCF8583        | Clock calendar with 240 x 8-bit RAM                                | 174  |

| PCF8593        | Low power clock/calendar                                           | 195  |

1998 Apr 29

# **SELECTION GUIDES**

|                    | Page |

|--------------------|------|

| Functional index   | 1:   |

| Selection guide    | 12   |

| Internet home page | 16   |

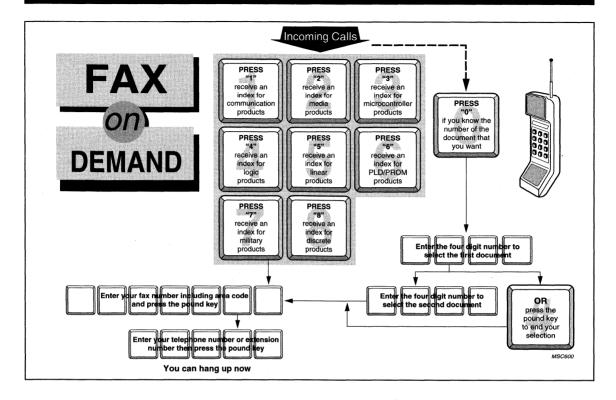

| Fax-on-Demand      | 17   |

# **CMOS Integrated Circuits** for Clocks and Watches

# **Functional index**

|                  |                                                                    | PAGE |

|------------------|--------------------------------------------------------------------|------|

| WATCHES          |                                                                    |      |

| PCA146X series   | 32 kHz watch circuit with adaptive motor pulse                     | 28   |

| PCA148X series   | 32 kHz watch circuit with adaptive motor pulse                     | 45   |

| PCA16XXseries    | 32 kHz watch circuit with EEProM                                   | 60   |

| PCA167Xseries    | 32 kHz watch circuit using a silver-oxide or a 3 V lithium battery | 69   |

| CAR CLOCKS       |                                                                    |      |

| PCF1171C         | 4-digit LCD car clock                                              | 75   |

| PCF1172C         | 3 1/2-digit LCD car clock                                          | 83   |

| PCF1174C         | 4-digit static LCD car clock                                       | 91   |

| PCF1175C         | 4-digit duplex LCD car clock                                       | 103  |

| PCF1178C         | 4-digit duplex LCD car clock                                       | 115  |

| PCF1179C         | 4-digit duplex LCD car clock                                       | 127  |

| REAL TIME CLOCKS |                                                                    |      |

| PCF8563          | Real time clock/calendar                                           | 139  |

| PCF8573          | Clock/calendar with power fail detector                            | 157  |

| PCF8583          | Clock calendar with 240 x 8-bit RAM                                | 174  |

| PCE8503          | Low nower clock/calendar                                           | 105  |

1998 Apr 29

# CMOS Integrated Circuits for Clocks, Watches and Real Time Clocks

# Selection guide

**ANALOG WATCH CIRCUITS: 32 KHZ**

Table 1 Watch circuits overview: PCA146x series

|               |                                   |                                 |                                          |               | SF                  | ECIFICATION | ONS                         |                               |      |

|---------------|-----------------------------------|---------------------------------|------------------------------------------|---------------|---------------------|-------------|-----------------------------|-------------------------------|------|

| TYPE #<br>PCA | DELIVERY<br>FORMAT <sup>(1)</sup> | PERIOD<br>t <sub>T</sub><br>(s) | PULSE<br>WIDTH<br>t <sub>p</sub><br>(ms) | DRIVE<br>(%)  | DETECT<br>CRITERION | EEPROM      | BATTERY<br>EOL<br>DETECTION | REMARKS                       | PAGE |

| 1461          | U; U10                            | 1                               | 7.8                                      | max.100<br>81 | P = 1<br>N = 2      | yes         | yes                         | 1.5 V and<br>2.1 V<br>Lithium | 28   |

| 1462          | U; U/7;<br>U/10                   | 1                               | 5.8                                      | max.100<br>81 | P = 1<br>N = 2      | yes         | yes                         | 1.5 V and<br>2.1 V<br>Lithium |      |

| 1463          | U; U/10                           | 1                               | 3.9                                      | max.100<br>81 | P = 1<br>N = 2      | yes         | yes                         | 1.5 V and<br>2.1 V<br>Lithium |      |

| 1465          | U/10; U/7                         | 1                               | 5.8                                      | max.100       | P = 1<br>N = 2      | yes         | no                          | 1.5 V                         |      |

| 1467          | U/10                              | 1                               | 7.8                                      | max.100       | P = 1<br>N = 2      | yes         | no                          | 1.5 V                         |      |

# Note

1. U = chip in tray; U/7 = chip with bumps on tape; U/10 = chip on foil.

Table 2 Watch circuits overview: PCA148x series

|               |                                   |                                 | SPECIFICATIONS                           |              |                     |        |                             |         |      |  |

|---------------|-----------------------------------|---------------------------------|------------------------------------------|--------------|---------------------|--------|-----------------------------|---------|------|--|

| TYPE #<br>PCA | DELIVERY<br>FORMAT <sup>(1)</sup> | PERIOD<br>t <sub>T</sub><br>(s) | PULSE<br>WIDTH<br>t <sub>P</sub><br>(ms) | DRIVE<br>(%) | DETECT<br>CRITERION | EEPROM | BATTERY<br>EOL<br>DETECTION | REMARKS | PAGE |  |

| 1485          | U/7                               | 1                               | 5.8                                      | 75           | P = 1<br>N = 2      | yes    | yes                         |         | 45   |  |

| 1486          | U/7                               | 1                               | 5.8                                      | 75           | P = 1<br>N = 2      | yes    | no                          |         |      |  |

| 1487          | U/5                               | 1                               | 7.8                                      | 75           | P = 2<br>N = 3      | yes    | yes                         |         |      |  |

## Note

1. U = Chip in trays; U/5 = wafer; U/7 = chip with bumps on tape.

# CMOS Integrated Circuits for Clocks, Watches and Real Time Clocks

# Selection guide

Table 3 Watch circuits overview: PCA16xx series

|               |                                   |                                 |                                          |              | SPECI  | FICATIONS                   |                               |      |

|---------------|-----------------------------------|---------------------------------|------------------------------------------|--------------|--------|-----------------------------|-------------------------------|------|

| TYPE #<br>PCA | DELIVERY<br>FORMAT <sup>(1)</sup> | PERIOD<br>t <sub>T</sub><br>(s) | PULSE<br>WIDTH<br>t <sub>P</sub><br>(ms) | DRIVE<br>(%) | EEPROM | BATTERY<br>EOL<br>DETECTION | REMARKS                       | PAGE |

| 1601          | U/10                              | 1                               | 7.8                                      | 100          | yes    | no                          |                               | 60   |

| 1602          | Т                                 | 1                               | 7.8                                      | 75           | yes    | no                          |                               |      |

| 1603          | U/7                               | 20                              | 7.8                                      | 100          | yes    | no                          |                               |      |

| 1604          | U/10                              | 5                               | 7.8                                      | 75           | yes    | no                          |                               |      |

| 1605          | U/7                               | 5                               | 4.8                                      | 75           | yes    | no                          |                               |      |

| 1606          | U/10                              | 10                              | 6.8                                      | 100          | yes    | no                          |                               |      |

| 1607          | U                                 | 5                               | 5.8                                      | 100<br>75    | yes    | no                          | 1.5 V and<br>2.1 V<br>Lithium |      |

| 1608          | U                                 | 5                               | 7.8                                      | 100<br>75    | yes    | no                          | 1.5 V and<br>2.1 V<br>Lithium |      |

| 1611          | U                                 | 1                               | 6.8                                      | 75           | yes    | no                          |                               |      |

| 1621          | U/7                               | 20                              | 4.8                                      | 100          | yes    | no                          |                               |      |

| 1622          | U                                 | 1                               | 4.8                                      | 100          | yes    | yes                         |                               |      |

| 1623          | U                                 | 20                              | 4.8                                      | 75           | yes    | no                          |                               |      |

| 1624          | U                                 | 12                              | 3.9                                      | 75<br>56     | yes    | no                          | 1.5 V and<br>2.1 V<br>Lithium |      |

| 1625          | U/7                               | 5                               | 5.8                                      | 75           | yes    | no                          |                               |      |

| 1626          | U                                 | 20                              | 5.8                                      | 100          | yes    | no                          |                               |      |

| 1627          | U/7                               | 20                              | 5.8                                      | 100<br>75    | yes    | no                          | 1.5 V and<br>2.1 V<br>Lithium |      |

| 1628          | U                                 | 20                              | 5.8                                      | 75           | yes    | no                          |                               |      |

| 1629          | U/7                               | 5                               | 6.8                                      | 75           | yes    | no                          |                               |      |

# Note

1. U = Chip in trays; U/7 = chip with bumps on tape; U/10 = chip on foil; T = SOT144-1.

# CMOS Integrated Circuits for Clocks, Watches and Real Time Clocks

Selection guide

Table 4 Watch circuits overview: PCA167x series

|               |                                   | PERIOD                |                                       |              | SPECIFIC | ATIONS                      |               |      |

|---------------|-----------------------------------|-----------------------|---------------------------------------|--------------|----------|-----------------------------|---------------|------|

| TYPE #<br>PCA | DELIVERY<br>FORMAT <sup>(1)</sup> | t <sub>T</sub><br>(s) | PULSE<br>WIDTH t <sub>P</sub><br>(ms) | DRIVE<br>(%) | EEPROM   | BATTERY<br>EOL<br>DETECTION | REMARKS       | PAGE |

| 1672          | U                                 | 1                     | 7.8                                   | 56           | no       | no                          | 3 V Lithium   | 69   |

| 1673          | U                                 | 1                     | 5.8                                   | 56           | no       | no                          | 3 V Lithium   |      |

| 1675          | U                                 | 1/16                  | 5.8                                   | 100          | no       | no                          | no oscillator |      |

| 1676          | U/10                              | 10                    | 5.8                                   | 56           | no       | no                          | 3 V Lithium   | ,    |

| 1677          | U                                 | 10                    | 7.8                                   | 100          | no       | no                          | 1.5 V         |      |

## Note

1. U = Chip in trays; U/10 = chip on foil.

# **DIGITAL CAR CLOCK CIRCUITS: 4.19 MHZ QUARTZ CRYSTAL**

Table 5 PCF1171C to PCF1179C overview.

|                |        |   | FUNCTIONS(1) TYPICAL |   |   |   |   |   |     |   |                           |           |      |

|----------------|--------|---|----------------------|---|---|---|---|---|-----|---|---------------------------|-----------|------|

| TYPE<br>NUMBER | DIGITS | A | В                    | С | D | E | F | G | н   | ı | SUPPLY<br>CURRENT<br>(µA) | REMARKS   | PAGE |

| PCF1171C       | 4      | • | •                    |   | • | • | • |   | •   |   | 400                       |           | 75   |

| PCF1172C       | 31/2   | • |                      | • | • | • | • |   | • , |   | 400                       |           | 83   |

| PCF1174C       | 4      | • | •                    | • | • | • | • |   | •   | • | 950                       | note 2    | 91   |

| PCF1175C       | 4      | • | •                    | • | • | • |   | • | •   | • | 950                       | note 2    | 103  |

| PCF1178C       | 4      | • | •                    | • | • | • |   | • | •   | • | 950                       | note 2    | 115  |

| PCF1179C       | 4      | • | •                    | • | • | • |   | • | •   | • | 950                       | note 2, 3 | 127  |

# **Notes**

1. Where columns A to I are the functions for:

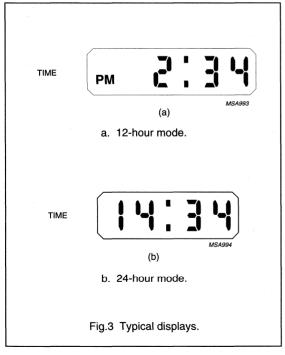

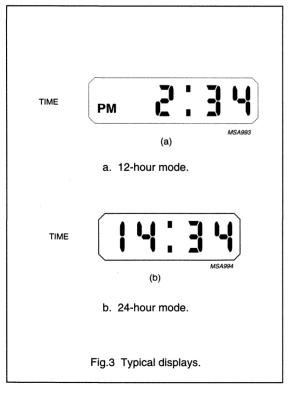

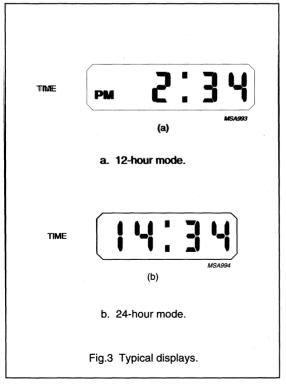

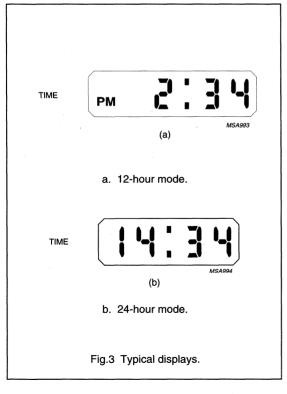

A = 12-hour mode

B = 24-hour mode

C = AM/PM annunciator

D = hours

E = minutes

F = direct drive

G = duplex drive

H = internal voltage regulator

I = EEPROM.

2. EEPROM for time calibration and voltage regulation of LCD.

3. Set mode with four advances per second.

# CMOS Integrated Circuits for Clocks, Watches and Real Time Clocks

# Selection guide

# REAL TIME CLOCK CIRCUITS (RTC)

Table 6 PCF8563 to PCF8593 overview

| TYPE<br>NUMBER | I <sup>2</sup> C-BUS | CLOCK OPERATING<br>SUPPLY VOLTAGE<br>(V) | PACKAGE     | REMARKS                                                                               | PAGE |

|----------------|----------------------|------------------------------------------|-------------|---------------------------------------------------------------------------------------|------|

| PCF8563        | yes ·                | 1.0 to 5.5                               | DIP8, SO8   | Provides year, month, day, weekday,<br>hours, minutes and seconds                     | 139  |

|                |                      |                                          |             | Century flag                                                                          |      |

|                |                      |                                          |             | Alarm and timer functions                                                             |      |

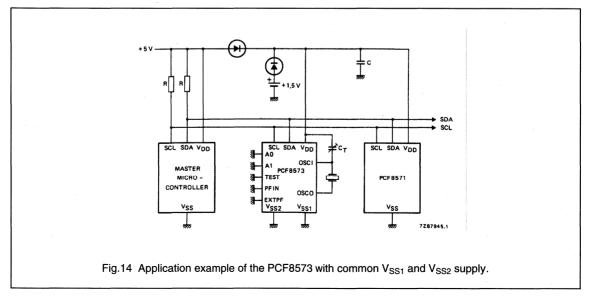

| PCF8573        | yes                  | 1.1 to 6.0                               | DIP16, SO16 | Provides month, day, hours and minutes                                                | 157  |

|                | -                    |                                          |             | On-chip power failure detector                                                        |      |

|                |                      |                                          |             | Alarm register for presetting a time or remote switching function                     |      |

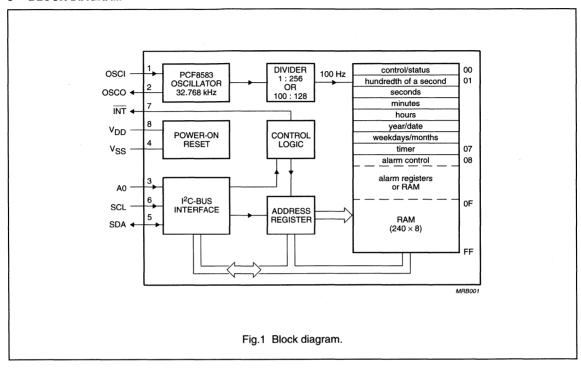

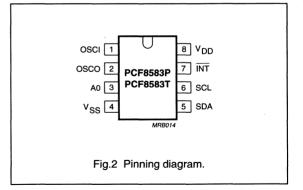

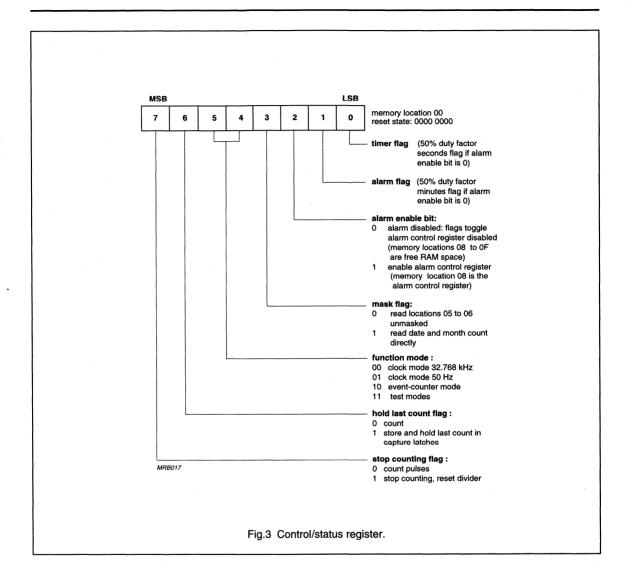

| PCF8583        | yes                  | 1.0 to 6.0                               | DIP8, SO8   | Provides month, day, weekday,                                                         | 174  |

|                |                      |                                          |             | hours, minutes, seconds and hundredths of seconds                                     |      |

|                |                      |                                          |             | ● 240 × 8-bit low-voltage RAM                                                         |      |

|                |                      |                                          | ·           | Universal timer with alarm and overflow indication                                    |      |

|                |                      |                                          |             | Automatic word address incrementing                                                   |      |

| PCF8593        | yes                  | 1.0 to 6.0                               | DIP8, SO8   | Provides month, day, weekday,<br>hours, minutes, seconds and<br>hundredths of seconds | 195  |

|                |                      |                                          |             | 8-byte scratchpad RAM (when alarm not used)                                           |      |

|                |                      |                                          |             | Universal timer with alarm and overflow indication                                    |      |

|                |                      |                                          |             | Automatic word address incrementing                                                   |      |

# **Internet World Wide Web Home Page**

# WHAT IS IT?

Welcome to our place in cyberspace.

Explore our Web pages and take a look at our product offering of advance High-performance Applications and Products.

In addition, we offer you the latest information on Products, News, Support, Employment and Offices.

# **HOW TO REACH US**

16

For access to the Philips Semiconductors Home Page go to the World Wide Web location:

http://www.semiconductors.philips.com/

1996 Nov 15

# **FAX-on-DEMAND System**

#### WHAT IS IT?

The FAX-on-DEMAND system is a computer facsimile system that allows customers to receive selected documents by fax automatically.

#### **HOW DOES IT WORK?**

To order a document, you simply enter the document number. This number can be obtained by asking for an index of available documents to be faxed to you the first time you call the system.

Our system has a selection of the latest product data sheets from Philips with varying page counts. As you know, it takes approximately one minute to FAX one page. This isn't bad if the number of pages is less than 10. But if the document is 37 pages long, be ready for a long transmission!

Philips Semiconductors also maintains product information on the World-Wide-Web. Our home page can be located at:

http://www.semiconductors.philips.com

# WHO DO I CONTACT IF I HAVE A QUESTION ABOUT FAX-ON-DEMAND?

Contact your local Philips sales office.

## **FAX-ON-DEMAND PHONE NUMBERS**

| United Kingdom, Ireland | 44-181-730-5020 |

|-------------------------|-----------------|

| France                  | 33-1-40-996060  |

| Italy                   | 39-167-295502   |

| North America           | 1-800-282-2000  |

# LOCATIONS SOON TO BE IN OPERATION

- Hong Kong

- Japan

- · The Netherlands.

# **GENERAL**

|                                                     | Page |

|-----------------------------------------------------|------|

| Quality                                             | 20   |

| Pro electron type numbering for integrated circuits | 21   |

| Rating systems                                      | 23   |

| Handling MOS devices                                | 25   |

General Quality

#### TOTAL QUALITY MANAGEMENT

Philips Semiconductors is a Quality Company, renowned for the high quality of our products and service. We keep alive this tradition by constantly aiming towards one ultimate standard, that of zero defects. This aim is guided by our Total Quality Management (TQM) system, the basis of which is described in the following paragraphs.

## **Quality assurance**

Based on ISO 9000 standards, customer standards such as Ford TQE and IBM MDQ. Our factories are certified to ISO 9000 by external inspectorates.

# Partnerships with customers

PPM co-operations, design-in agreements, ship-to-stock, just-in-time and self-qualification programmes, and application support.

# Partnerships with suppliers

Ship-to-stock, statistical process control and ISO 9000 audits.

# Quality improvement programme

Continuous process and system improvement, design improvement, complete use of statistical process control, realization of our final objective of zero defects, and logistics improvement by ship-to-stock and just-in-time agreements.

# **ADVANCED QUALITY PLANNING**

During the design and development of new products and processes, quality is built-in by advanced quality planning. Through failure-mode-and-effect analysis the critical parameters are detected and measures taken to ensure good performance on these parameters. The capability of process steps is also planned in this phase.

#### PRODUCT CONFORMANCE

The assurance of product conformance is an integral part of our quality assurance (QA) practice. This is achieved by:

- Incoming material management through partnerships with suppliers.

- In-line quality assurance to monitor process reproducibility during manufacture and initiate any necessary corrective action. Critical process steps are 100% under statistical process control.

- Acceptance tests on finished products to verify conformance with the device specification. The test results are used for quality feedback and corrective actions. The inspection and test requirements are detailed in the general quality specifications.

- Periodic inspections to monitor and measure the conformance of products.

# PRODUCT RELIABILITY

With the increasing complexity of Original Equipment Manufacturer (OEM) equipment, component reliability must be extremely high. Our research laboratories and development departments study the failure mechanisms of semiconductors. Their studies result in design rules and process optimization for the highest built-in product reliability. Highly accelerated tests are applied to the products reliability evaluation. Rejects from reliability tests and from customer complaints are submitted to failure analysis, to result in corrective action.

# **CUSTOMER RESPONSES**

Our quality improvement depends on joint action with our customer. We need our customer's inputs and we invite constructive comments on all aspects of our performance. Please contact our local sales representative.

# RECOGNITION

The high quality of our products and services is demonstrated by many Quality Awards granted by major customers and international organizations.

# General

# Pro electron type numbering of integrated circuits

#### **BASIC TYPE NUMBER**

This type designation code applies to semiconductor monolithic, semiconductor multi-chip, thin film, thick film and hybrid integrated circuits. The basic type number comprises three letters followed by a serial number.

#### First and second letters

DIGITAL FAMILY CIRCUITS

The first two letters identify the family.(1)

SOLITARY CIRCUITS

The first letter divides solitary circuits into:

S Solitary digital circuits

T Analog circuits

U Mixed analog/digital circuits.

The second letter is a serial letter without any further significance except 'H' which stands for hybrid circuits.(2)

#### **MICROPROCESSORS**

The first two letters identify microprocessors and related circuits:

MA Microcomputer or central processing unit

MB Slice processor (functional slice of microprocessor)

MD Related memories

ME Other related circuits such as interfaces, clocks, peripheral controllers, etc.

CHARGE-TRANSFER DEVICES AND SWITCHED CAPACITORS

The first two letters identify:

NH Hybrid circuits

NL Logic circuits

NM Memories

NS Analog signal processing using switched capacitors

NT Analog signal processing using charge-transfer devices

NX Imaging devices

NY Other related circuits.

#### Third letter

The third letter indicates the operating ambient temperature range:

A temperature range not specified below

B 0 to +70 °C

C -55 to +125 °C

D -25 to +70 °C

E -25 to +85 °C

F -40 to +85 °C

G -55 to +85 °C.

If a device has another temperature range, the letter 'A' or a letter indicating a narrower temperature may be used, for example, the range of 0 to +75 °C can be indicated by 'A' or 'B'. Should two devices with the same basic type number both have temperature ranges other than those specified, one would use the letter 'A' and the other the letter 'X'.

## **SERIAL NUMBER**

This may be a four-digit number assigned by Pro Electron, or the serial number (which may be a combination of figures and letters) of an existing company type designation of the manufacturer.

#### **VERSION LETTER**

A single version letter may be added to the basic type number. This indicates a minor variant of the basic type or the package. The version letter has no fixed meaning except for 'Z' which means customized wiring. The following letters are recommended for package variants:

- C Cylindrical

- D Ceramic dual in-line (CERDIL, CERDIP)

- F Flat pack (two leads)

- G Flat pack (four leads)

- H Quad flat pack (QFP)

- L Chip on tape (foil)

- P Plastic dual in-line (DIL)

- Q Quad in-line (QUIL)

- T Mini pack (SOL, SO, VSO)

- U Uncased chip.

<sup>(1)</sup> A logic family is an assembly of digital circuits designed to be interconnected and defined by its base electrical characteristics, such as supply voltage, power consumption, propagation delay, noise immunity.

<sup>(2)</sup> The first letter 'S' should be used for all solitary memories, to which, in the event of hybrids, the second letter 'H' should be added, for example, SH for bubble memories.

# Pro electron type numbering of integrated circuits

# General

#### **TWO-LETTER SUFFIX**

A two-letter suffix may be used instead of a single package version letter to give more information. To avoid confusion with serial numbers that end with a letter, a hyphen should precede the suffix.

# First letter (general shape)

- C Cylindrical

- D Dual in-line (DIL)

- E Power DIL (with external heatsink)

- F Flat pack (leads on two sides)

- G Flat pack (leads on four sides)

- H Quad flat pack (QFP)

- K Diamond (TO-3 family)

- M Multiple in-line (except dual, triple and quad)

- Q Quad in-line (QUIL)

- R Power QUIL (with external heatsink)

- S Single in-line (SIL)

- T Triple in-line

- W Leaded chip carrier (LCC)

- X Leadless chip carrier (LLCC)

- Y Pin grid array (PGA).

# Second letter (material)

- C Metal-ceramic

- G Glass-ceramic

- M Metal

- P Plastic.

#### **EXAMPLES**

PCF1105WP: digital IC; PC family; operating temperature range –40 to +85 °C; serial number 1105; plastic leaded chip carrier.

GMB74LS00A-DC: digital IC; GM family; operating temperature range 0 to +70 °C; company number 74LS00A; ceramic DIL package.

TDA1000P: analog IC; operating temperature range non-standard; serial number 1000; plastic DIL package.

SAC2000: solitary digital circuit; operating temperature range –55 to +125 °C; serial number 2000.

# General

# **Rating systems**

#### **RATING SYSTEMS**

The rating systems described are those recommended by the IEC in its publication number 134.

#### **Definitions of terms used**

#### ELECTRONIC DEVICE

An electronic tube or valve, transistor or other semiconductor device. This definition excludes inductors, capacitors, resistors and similar components.

#### CHARACTERISTIC

A characteristic is an inherent and measurable property of a device. Such a property may be electrical, mechanical, thermal, hydraulic, electro-magnetic or nuclear, and can be expressed as a value for stated or recognized conditions. A characteristic may also be a set of related values, usually shown in graphical form.

#### BOGEY ELECTRONIC DEVICE

An electronic device whose characteristics have the published nominal values for the type. A bogey electronic device for any particular application can be obtained by considering only those characteristics that are directly related to the application.

## **RATING**

A value that establishes either a limiting capability or a limiting condition for an electronic device. It is determined for specified values of environment and operation, and may be stated in any suitable terms. Limiting conditions may be either maxima or minima.

#### RATING SYSTEM

The set of principles upon which ratings are established and which determine their interpretation. The rating system indicates the division of responsibility between the device manufacturer and the circuit designer, with the object of ensuring that the working conditions do not exceed the ratings.

# Absolute maximum rating system

Absolute maximum ratings are limiting values of operating and environmental conditions applicable to any electronic device of a specified type, as defined by its published data, which should not be exceeded under the worst probable conditions.

These values are chosen by the device manufacturer to provide acceptable serviceability of the device, taking no responsibility for equipment variations, environmental variations, and the effects of changes in operating conditions due to variations in the characteristics of the device under consideration and of all other electronic devices in the equipment.

The equipment manufacturer should design so that, initially and throughout the life of the device, no absolute maximum value for the intended service is exceeded with any device, under the worst probable operating conditions with respect to supply voltage variation, equipment component variation, equipment control adjustment, load variations, signal variation, environmental conditions, and variations in characteristics of the device under consideration and of all other electronic devices in the equipment.

## Design maximum rating system

Design maximum ratings are limiting values of operating and environmental conditions applicable to a bogey electronic device of a specified type as defined by its published data, and should not be exceeded under the worst probable conditions.

These values are chosen by the device manufacturer to provide acceptable serviceability of the device, taking responsibility for the effects of changes in operating conditions due to variations in the characteristics of the electronic device under consideration.

The equipment manufacturer should design so that, initially and throughout the life of the device, no design maximum value for the intended service is exceeded with a bogey electronic device, under the worst probable operating conditions with respect to supply voltage variation, equipment component variation, variation in characteristics of all other devices in the equipment, equipment control adjustment, load variation, signal variation and environmental conditions.

## Design centre rating system

Design centre ratings are limiting values of operating and environmental conditions applicable to a bogey electronic device of a specified type as defined by its published data, and should not be exceeded under normal conditions.

General Rating systems

These values are chosen by the device manufacturer to provide acceptable serviceability of the device in average applications, taking responsibility for normal changes in operating conditions due to rated supply voltage variation, equipment component variation, equipment control adjustment, load variation, signal variation, environmental conditions, and variations in the characteristics of all electronic devices.

The equipment manufacturer should design so that, initially, no design centre value for the intended service is exceeded with a bogey electronic device in equipment operating at the stated normal supply voltage.

# General

# **Handling MOS devices**

#### **ELECTROSTATIC CHARGES**

Electrostatic charges can exist in many things; for example, man-made-fibre clothing, moving machinery, objects with air blowing across them, plastic storage bins, sheets of paper stored in plastic envelopes, paper from electrostatic copying machines, and people. The charges are caused by friction between two surfaces, at least one of which is non-conductive. The magnitude and polarity of the charges depend on the different affinities for electrons of the two materials rubbing together, the friction force and the humidity of the surrounding air.

Electrostatic discharge is the transfer of an electrostatic charge between bodies at different potentials and occurs with direct contact or when induced by an electrostatic field. All of our MOS devices are internally protected against electrostatic discharge but they **can** be damaged if the following precautions are not taken.

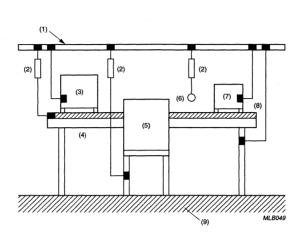

#### WORK STATION

Figure 1 shows a working area suitable for safely handling electrostatic sensitive devices. It has a work bench, the surface of which is conductive or covered by an antistatic sheet. Typical resistivity for the bench surface is between 1 and 500 k $\Omega$  per cm<sup>2</sup>. The floor should also be covered with antistatic material. The following precautions should be observed:

- Persons at a work bench should be earthed via a wrist strap and a resistor.

- All mains-powered electrical equipment should be connected via an earth leakage switch.

- · Equipment cases should be earthed.

- Relative humidity should be maintained between 50 and 65%.

- An ionizer should be used to neutralize objects with immobile static charges.

#### RECEIPT AND STORAGE

MOS devices are packed for dispatch in antistatic/conductive containers, usually boxes, tubes or blister tape. The fact that the contents are sensitive to electrostatic discharge is shown by warning labels on both primary and secondary packing.

The devices should be kept in their original packing whilst in storage. If a bulk container is partially unpacked, the unpacking should be performed at a protected work station. Any MOS devices that are stored temporarily should be packed in conductive or antistatic packing or carriers.

# **ASSEMBLY**

MOS devices must be removed from their protective packing with earthed component pincers or short-circuit clips. Short-circuit clips must remain in place during mounting, soldering and cleansing/drying processes. Do not remove more devices from the storage packing than are needed at any one time. Production/assembly documents should state that the product contains electrostatic sensitive devices and that special precautions need to be taken.

During assembly, ensure that the MOS devices are the last of the components to be mounted and that this is done at a protected work station.

All tools used during assembly, including soldering tools and solder baths, must be earthed. All hand tools should be of conductive or antistatic material and, where possible, should not be insulated.

Measuring and testing of completed circuit boards must be done at a protected work station. Place the soldered side of the circuit board on conductive or antistatic foam and remove the short-circuit clips. Remove the circuit board from the foam, holding the board only at the edges. Make sure the circuit board does not touch the conductive surface of the work bench. After testing, replace the circuit board on the conductive foam to await packing.

Assembled circuit boards containing MOS devices should be handled in the same way as unmounted MOS devices. They should also carry warning labels and be packed in conductive or antistatic packing.

# General

- (1) Earthing rail.

- (2) Resistor (500 k $\Omega$  ± 10%, 0.5 W).

- (3) Ionizer.

- (4) Work bench.

- (5) Chair.

- (6) Wrist strap.

- (7) Electrical equipment.

- (8) Conductive surface/antistatic sheet.

- (9) Antistatic floor.

Fig.1 Protected work station.

# **DEVICE DATA**

(in alphanumeric sequence)

# PCA146x series

# **FEATURES**

- 32 kHz oscillator, amplitude regulated with excellent frequency stability

- · High immunity of the oscillator to leakage currents

- Time calibration electrically programmable and reprogrammable (via EEPROM)

- · A quartz crystal is the only external component required

- · Very low current consumption; typically 170 nA

- Output for bipolar stepping motors of different types

- Up to 50% reduction in motor current compared with conventional circuits, by self adaption of the motor pulse width to match the required torque of the motor

- No loss of motor steps possible because of on-chip detection of the induced motor voltage

- · Detector for lithium or silver-oxide battery voltage levels

- · Indication for battery end-of-life

- · Stop function for accurate timing

- · Power-on reset for fast testing

- Various test modes for testing the mechanical parts of the watch and the IC.

# **GENERAL DESCRIPTION**

The PCA146x series devices are CMOS integrated circuits specially suited for battery-operated, quartz-crystal-controlled wrist-watches, with a bipolar stepping motor.

# ORDERING INFORMATION

| TYPE        |      | PACKAGE <sup>(1)</sup>  |         |

|-------------|------|-------------------------|---------|

| NUMBER      | NAME | DESCRIPTION             | VERSION |

| PCA1461U    | -    | chip in tray            | -       |

| PCA1461U/10 | -    | chip on foil            | _       |

| PCA1462U    | _    | chip in tray            | _       |

| PCA1462U/7  | -    | chip with bumps on tape | _       |

| PCA1462U/10 | -    | chip on foil            | _       |

| PCA1463U    | -    | chip in tray            | -       |

| PCA1463U/10 | -    | chip on foil            | -       |

| PCA1465U/10 | -    | chip on foil            | _       |

| PCA1465U/7  | _    | chip with bumps on tape | _       |

| PCA1467U/10 |      | chip on foil            | _       |

# Note

Figure 1 and Chapter "Package outline" show details of standard package, available for large orders only.

Chapter "Chip dimensions and bonding pad locations" shows exact pad locations for other delivery formats.

# PCA146x series

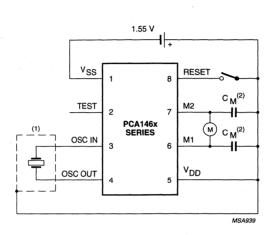

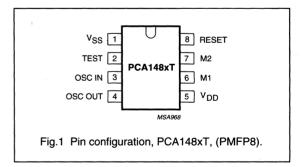

#### **PINNING**

| SYMBOL          | PIN | DESCRIPTION       |

|-----------------|-----|-------------------|

| V <sub>SS</sub> | 1   | ground (0 V)      |

| TEST            | 2   | test output       |

| OSC IN          | 3   | oscillator input  |

| OSC OUT         | 4   | oscillator output |

| $V_{DD}$        | 5   | supply voltage    |

| M1              | 6   | motor 1 output    |

| M2              | 7   | motor 2 output    |

| RESET           | 8   | reset input       |

# VSS 1 TEST 2 OSC IN 3 OSC OUT 4 Fig.1 Pin configuration, PCA146xT, (PMFP8).

# **FUNCTIONAL DESCRIPTION AND TESTING**

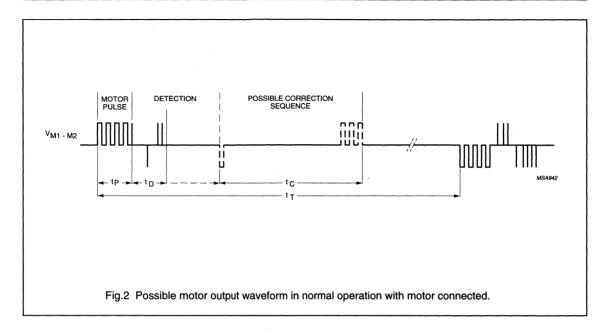

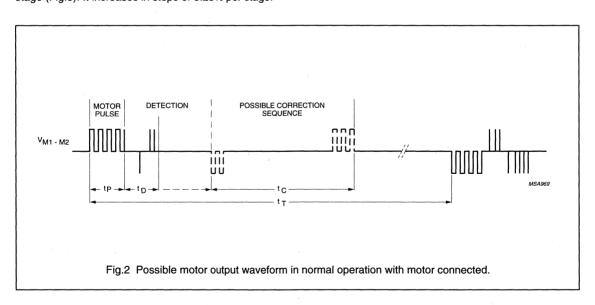

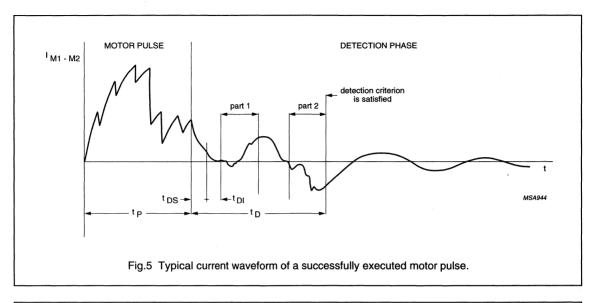

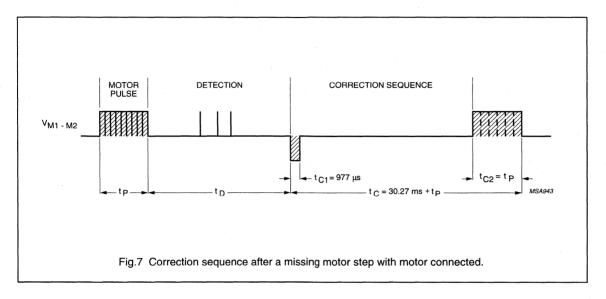

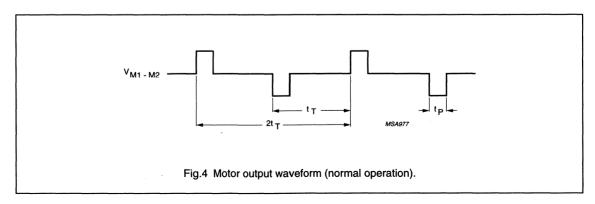

The motor output delivers pulses of six different stages depending on the torque required to turn the motor (Figs. 3 and 4). Every motor pulse is followed by a detection phase which monitors the waveform of the induced motor voltage. When a step is missed a correction sequence will be started (Fig.2).

# **Motor pulses**

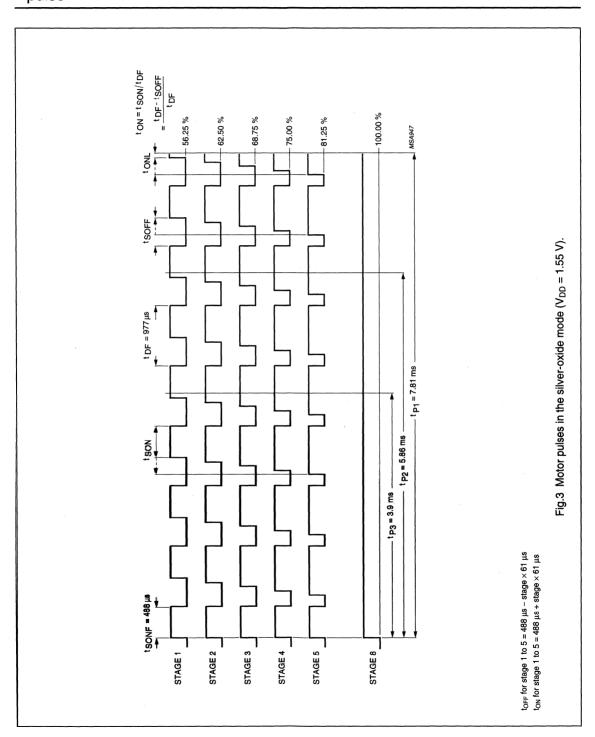

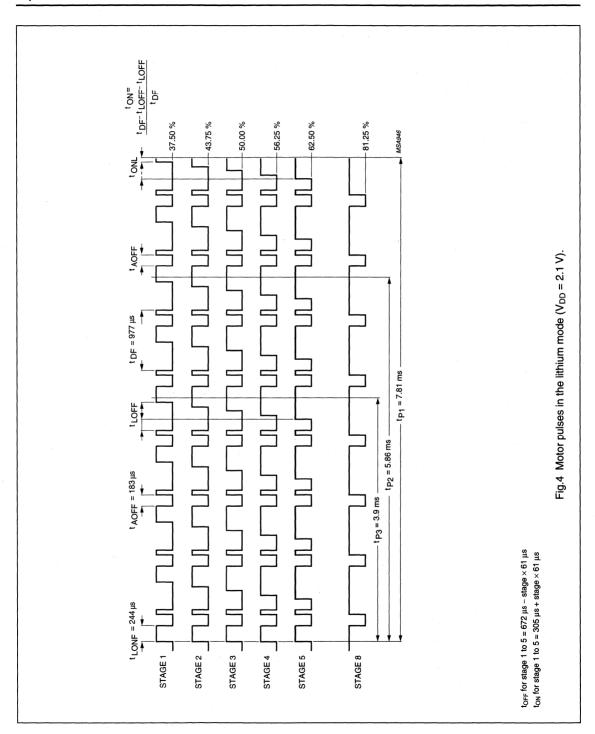

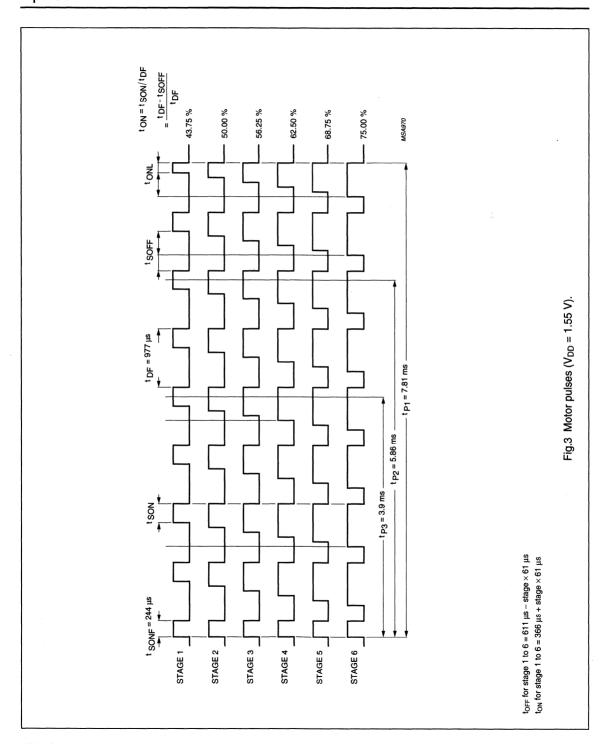

The circuit produces motor pulses of six different stages (stage 1 to 5, stage 8). Each stage has two independent modes: silver-oxide and lithium. The voltage level of  $V_{DD}$  determines which mode is selected (see Section "Voltage level detector").

Stages 1 to 5 (both modes) are used in normal operation, stage 8 occurs under the following conditions:

- Correction pulse after a missing step (both modes)

- · End-of-life mode

- If stage 5 is not enough to turn the motor (both modes):

In the silver-oxide mode, the ON state of the motor pulse varies between 56.25% and 100% of the duty factor  $t_{DF}=977~\mu s$  depending on the stage (Fig.3). It increases in steps of 6.25% per stage.

In the lithium mode, the ON state of the motor pulse is reduced by 18.75% of the duty factor  $t_{DF}$  (Fig.4) to compensate for the increase in the voltage level.

After a RESET the circuit always starts and continues with stage 1, when all motor pulses have been executed. A failure to execute all motor pulses results in the circuit going into stage 2, this sequence will be repeated through to stage 8.

When the motor pulses at stage 5 are not large enough to turn the motor, stage 8 is implemented for a maximum of 8 minutes with no attempt to keep current consumption low. After stage 8 has been executed the procedure is repeated from RESET.

The circuit operates for 8 minutes at a fixed stage, if every motor pulse is executed. The next 480 motor pulses are then produced at the next lower stage unless a missing step is detected. If a step is missed a correction sequence is produced and for a maximum of 8 minutes the motor pulses are increased by one stage.

# PCA146x series

PCA146x series

# PCA146x series

١

# PCA146x series

# Voltage level detector

The supply voltage is compared with the internal voltage reference  $V_{\text{LIT}}$  and  $V_{\text{EOL}}$  every minute. The first voltage level detection is carried out 30 ms after RESET.

When a lithium voltage level is detected  $(V_{DD} \ge V_{LIT})$ , the circuit starts operating in the lithium mode (Fig.4).

When the detected  $V_{DD}$  voltage level is between  $V_{LIT}$  and  $V_{EOL}$ , the circuit operates in the silver-oxide mode (Fig.3).

If the battery end-of-life is detected ( $V_{DD} < V_{EOL}$ ), the detection and stage control is switched OFF and the waveform produced is an unchopped version of the stage 8 waveform. To indicate this condition the waveform is produced in bursts of 4 pulses every 4 s.

## **Detection of motor movement**

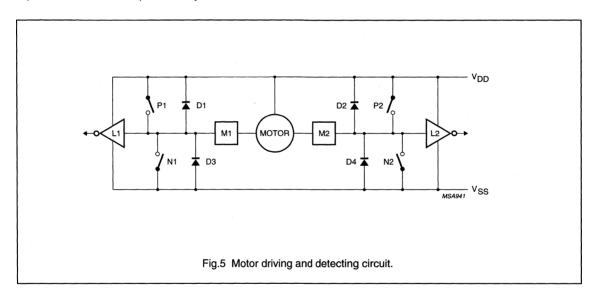

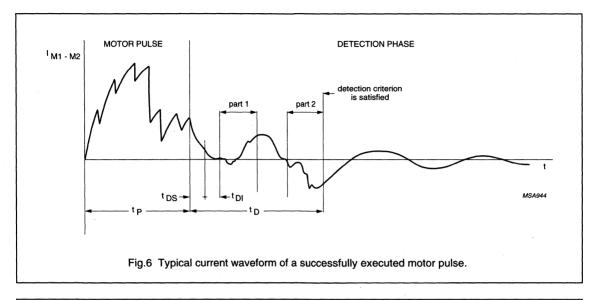

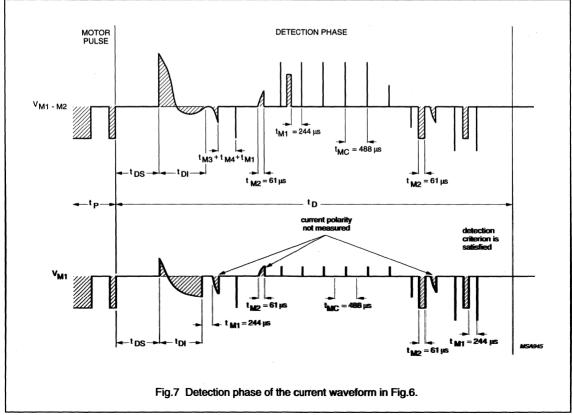

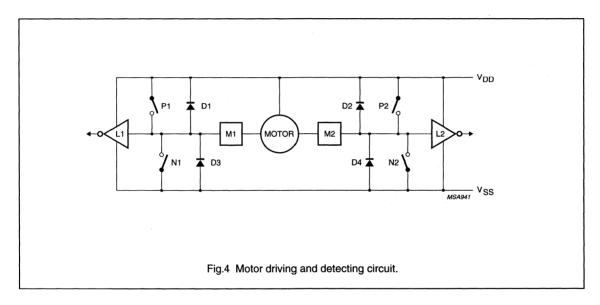

After a motor pulse, the motor is short-circuited to  $V_{DD}$  for 1 ms. Afterwards the energy in the motor inductor will be dissipated to measure only the current generated by the induced motor voltage. During the time  $t_{DI}$  (dissipation of energy time) all switches shown in Fig.5 are open to reduce the current as fast as possible. The current will now flow through the diodes D3 and D2, or D4 and D1. Then the first of 52 possible measurement cycles ( $t_{MC}$ ) starts to measure the induced current.

# PCA146x series

#### **Detection criteria**

The PCA146x uses current detection in two defined parts of the detection phase to determine if the motor has moved (refer to Figs 6 and 7). The detection criteria are:

# part 1

Minimum value of P = 1; where P = number of measured positive current polarities after t<sub>DI</sub>.

# part 2

Minimum value of N = 2; where N = number of measured positive current polarities since the first negative current polarity after part 1 was detected (see Fig.6).

If the opposite polarity is measured in one part, the internal counter is reset, so the results of all measurements in this part are ignored. The waveform of the induced current must enable all these measurements within the time  $t_D$  after the end of a positive motor pulse in order to be accepted as a waveform of an executed motor pulse.

If the detection criterion is satisfied earlier, a measurement cycle will not be started and the switches P1 and P2 stay closed, the motor is switched to  $V_{\rm DD}$ .

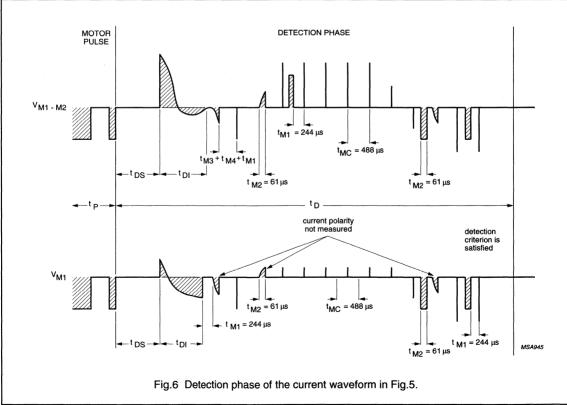

Every measurement cycle  $(t_{MC})$  has 4 phases. These are detailed in Table 1.

Note that detection and pulse width control will be switched OFF when the battery voltage is below the end-of-life voltage ( $V_{EOL}$ ), or if stage 5 is not sufficient to turn the motor

Table 1 Measurement cycle

| SYMBOL          | PHASE | DESCRIPTION                                                                                                                                                                                                                                             |

|-----------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>M1</sub> | 1     | During $t_{M1}$ the switches P1 and P2 are closed in order to switch the motor to $V_{DD}$ , so the induced current flows unaffected through the motor inductance.                                                                                      |

| t <sub>M2</sub> | 2     | Measures the induced current; during a maximum time $t_{M2}$ all switches are open until a change is sensed by one of the level detectors (L1, L2). The motor is short-circuited to $V_{DD}$ .                                                          |

|                 |       | Depending on the direction of the interrupted current:                                                                                                                                                                                                  |

|                 |       | • The current flows through diodes D3 and D2, causing the voltage at M1 to decrease in relation to M2;                                                                                                                                                  |

|                 |       | • The current flows through diodes D4 and D1, causing the voltage at M2 to decrease in relation to M1.                                                                                                                                                  |

|                 |       | A successfully detected current polarity is normally characterized by a short pulse of 0.5 to 10 $\mu$ s with a voltage up to $\pm 2.1$ V, failed polarity detection by the maximum pulse width of 61 $\mu$ s and a voltage of $\pm 0.5$ V (see Fig.7). |

| t <sub>M3</sub> | 3     | The switches P1 and P2 remain closed for the time t <sub>M3</sub> .                                                                                                                                                                                     |

| t <sub>M4</sub> | 4     | If the circuit detects fewer pulses than P and N respectively, a pulse of the time t <sub>M4</sub> occurs to reduce the induced current. Therefore P2 and P1 are opened and N1 and N2 are closed. Otherwise P1 and P2 remain closed.                    |

# PCA146x series

# PCA146x series

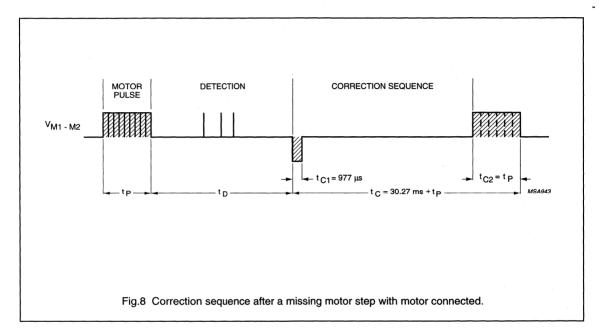

# Correction sequence (see Fig.8)

If a missing step is detected, a correction sequence is produced. This consists of a small pulse ( $t_{C1}$ ) which gives the motor a defined position and after 29.30 ms a pulse of stage 8 ( $t_{C2}$ ) to turn the motor.

# PCA146x series

#### Time calibration

Taking a normal quartz crystal with frequency 32768kHz, frequency deviation ( $\Delta f/f$ ) of  $\pm 15 \times 10^{-6}$  and  $C_L = 8.2$  pF; the oscillator frequency is offset (by using non-symmetrical internal oscillator input and output capacitances of 10 pF and 15 pF) such that the frequency deviation is positive-only. This positive deviation can then be compensated for to maintain time-keeping accuracy.

Once the positive frequency deviation is measured, a corresponding number 'n' (see Table 2) can be programmed into the device's EEPROM. This causes n pulses of frequency 8192 Hz to be inhibited every minute of operation, which achieves the required calibration.

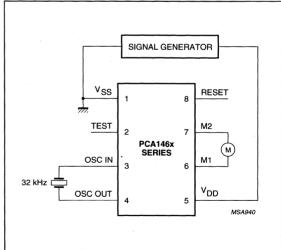

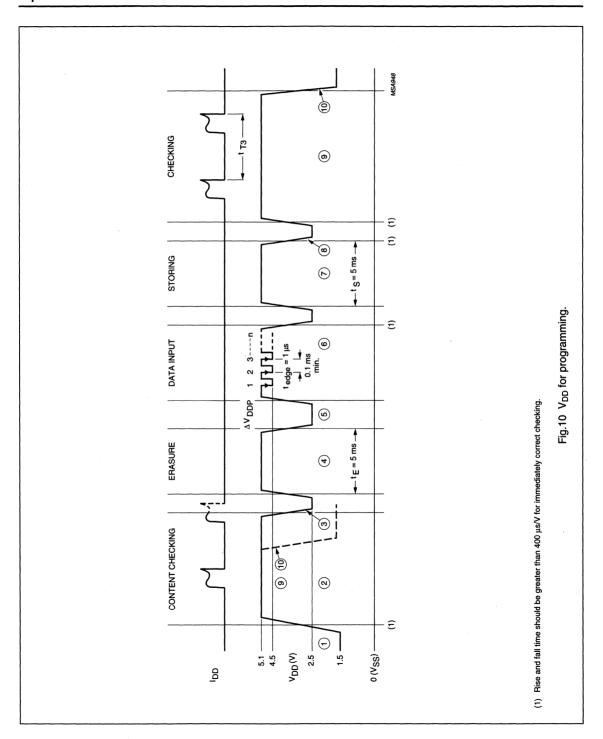

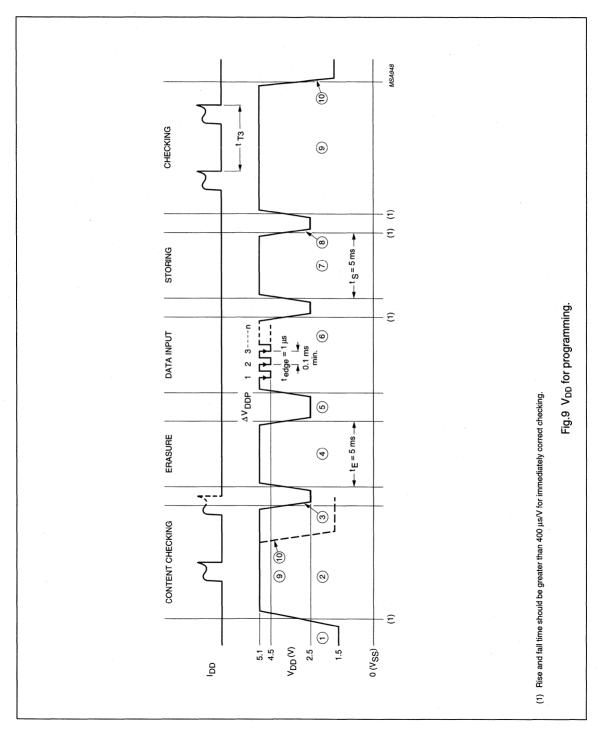

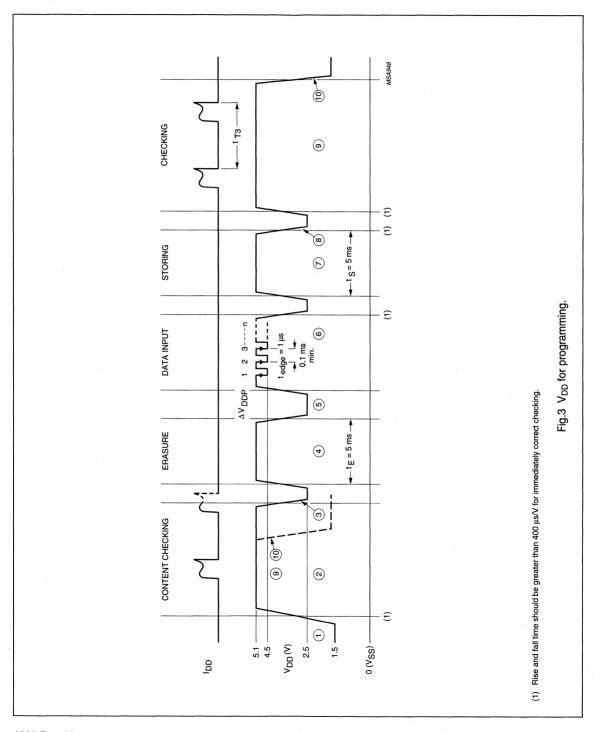

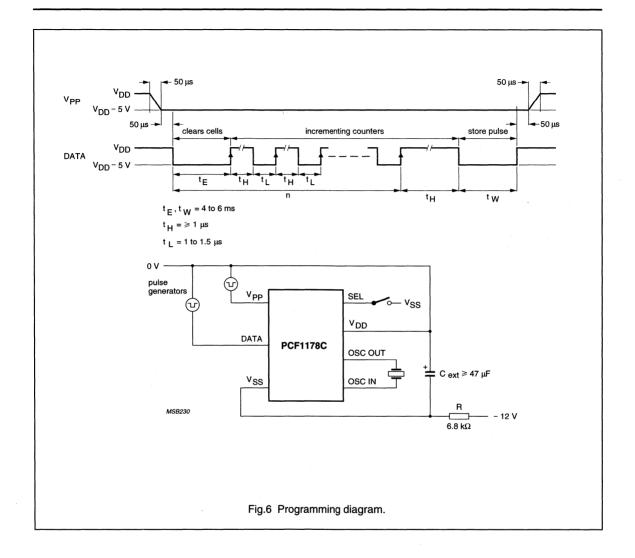

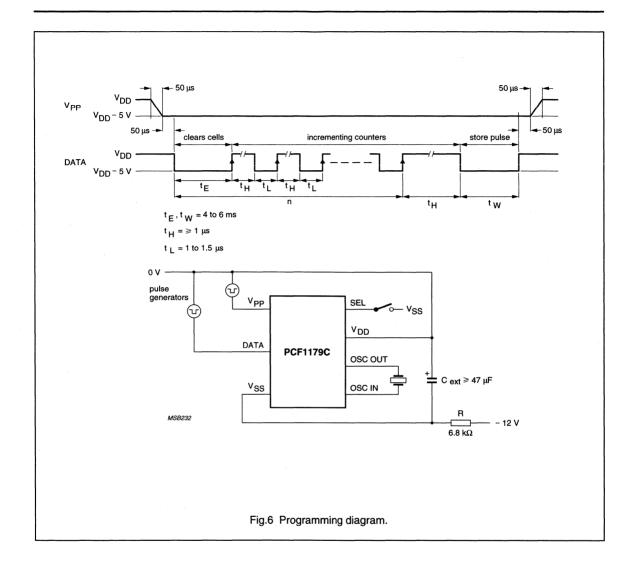

The programming circuit is shown in Fig.9. The required number n is programmed into EEPROM by varying  $V_{DD}$  according to the steps shown in Fig.10, which are explained below:

- The positive quartz frequency deviation (Δf/f) is measured, and the corresponding values of n are found according to Table 2.

- 2.  $V_{DD}$  is increased to 5.1 V allowing the contents of the EEPROM to be checked from the motor pulse period  $t_{T3}$  at nominal frequency.

**Table 2** Quartz crystal frequency deviation, n and t<sub>T3</sub>

| FREQUENCY<br>DEVIATION<br>$\Delta f/f$<br>(× 10 <sup>-6</sup> ) | EVIATION NUMBER OF PULSES |                       |

|-----------------------------------------------------------------|---------------------------|-----------------------|

| 0(1)                                                            | 0                         | 31.250 <sup>(2)</sup> |

| +2.03                                                           | 1                         | 31.372                |

| +4.06                                                           | 2                         | 31.494                |

| .•                                                              |                           |                       |

|                                                                 |                           |                       |

|                                                                 |                           |                       |

| +127.89                                                         | 63                        | 38.936                |

# Notes

- 1. Increments of  $2.03 \times 10^{-6}$ /step.

- 2. Increments of 122 μs/step.

- 3. V<sub>DD</sub> is decreased to 2.5 V during a motor pulse to initialize a storing sequence.

- 4. The first  $V_{DD}$  pulse to 5.1 V erases the contents of EEPROM.

- When the EEPROM is erased a logic 1 is at the TEST pin.

- 6.  $V_{DD}$  is increased to 5.1 V to read the data by pulsing  $V_{DD}$  n times to 4.5 V. After the n edge,  $V_{DD}$  is decreased to 2.5 V.

- V<sub>DD</sub> is increased to 5.1 V to store n bits in the EEPROM.

- 8. V<sub>DD</sub> is decreased to 2.5 V to terminate the storing sequence and to return to operating mode.

- 9.  $V_{DD}$  is increased to 5.1 V to check writing from the motor pulse period  $t_{T3}$ .

- V<sub>DD</sub> is decreased to the operation voltage **between** two motor pulses to return to operating mode. (Decreasing V<sub>DD</sub> during the motor pulse would restart the programming mode).

The time calibration can be reprogrammed up to 100 times.

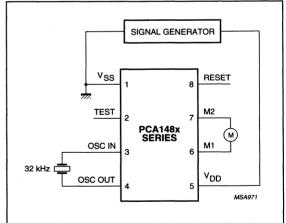

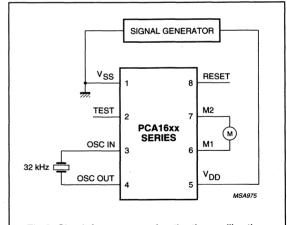

Fig.9 Circuit for programming the time calibration.

# PCA146x series

Product specification

# PCA146x series

#### Power-on reset

For correct operation of the Power-on reset the rise time of  $V_{DD}$  from 0 V to 2.1 V should be less than 0.1 ms. All resetable flip-flops are reset. Additionally the polarity of the first motor pulse is positive:  $V_{M1} - V_{M2} \ge 0$  V.

## **Customer testing**

An output frequency of 32 Hz is provided at RESET (pin 8) to be used for exact frequency measurement. Every minute a jitter occurs as a result of the inhibition, which occurs 90 to 150 ms after disconnecting the RESET from  $V_{\rm DD}$ .

Connecting the RESET to  $V_{DD}$  stops the motor pulses leaving them in a 3-state mode and sets the motor pulse width for the next available motor pulse to stage 1 in the silver-oxide mode. A 32 Hz signal without jitter is produced at the TEST pin.

Debounce time RESET = 14.7 to 123.2 ms.

Connecting RESET to  $V_{SS}$  activates Tests 1 and 2 and disables the inhibition.

**Test 1, V<sub>DD</sub> > V<sub>EOL</sub>**. Normal function takes place except that the motor pulse period is  $t_{T1} = 125$  ms instead of  $t_{T}$ , and the motor pulse stage is reduced every second instead of every 8 minutes. At TEST a speeded-up 8 minute signal is available.

Test 2,  $V_{DD}$  <  $V_{EOL}$ . Motor pulses of stage 8 are produced, with a time period of  $t_{T2}$  = 31.25 ms.

Test and reset modes are terminated by disconnecting the RESET pin.

Test 3,  $V_{DD}$  > 5.1 V. Motor pulses of stage 8 are produced, with a time period of  $t_{T3}$  = 31.25 ms and n × 122  $\mu$ s to check the contents of the EEPROM. At TEST a speeded-up cycle for motor pulse period signal  $t_T$  is available at 1024 times its normal frequency. Decreasing  $V_{DD}$  voltage level to lower than 2.5 V between two motor pulses returns the circuit to normal operating conditions.

#### **AVAILABLE TYPES**

Refer to Chapters "Ordering information" and "Functional description and testing".

|                         |                                   |                                 | SPECIFICATIONS                           |                |                        |        |                             |                            |

|-------------------------|-----------------------------------|---------------------------------|------------------------------------------|----------------|------------------------|--------|-----------------------------|----------------------------|

| SHORT<br>TYPE<br>NUMBER | DELIVERY<br>FORMAT <sup>(1)</sup> | PERIOD<br>t <sub>T</sub><br>(s) | PULSE<br>WIDTH<br>t <sub>P</sub><br>(ms) | DRIVE<br>(%)   | DETECTION<br>CRITERION | EEPROM | BATTERY<br>EOL<br>DETECTION | REMARKS                    |

| 1461                    | U; U/10                           | 1                               | 7.8                                      | max. 100<br>81 | P = 1<br>N = 2         | yes    | yes                         | 1.5 V and<br>2.1 V Lithium |

| 1462                    | U; U/7;<br>U/10                   | 1                               | 5.8                                      | max. 100<br>81 | P = 1<br>N = 2         | yes    | yes                         | 1.5 V and<br>2.1 V Lithium |

| 1463                    | U; U/10                           | 1                               | 3.9                                      | max. 100<br>81 | P = 1<br>N = 2         | yes    | yes                         | 1.5 V and<br>2.1 V Lithium |

| 1465                    | U/10; U/7                         | 1                               | 5.8                                      | max. 100       | P = 1<br>N = 2         | yes    | no                          | 1.5 V                      |

| 1467                    | U/10                              | 1                               | 7.8                                      | max. 100       | P = 1<br>N = 2         | yes    | no                          | 1.5 V                      |

#### Note

1. U = Chip in tray; U/7 = chip with bumps on tape; U/10 = chip on foil.

Philips Semiconductors Product specification

# 32 kHz watch circuits with adaptive motor pulse

PCA146x series

## **LIMITING VALUES**

In accordance with the Absolute Maximum Rating System (IEC 134).

| SYMBOL           | PARAMETER                     | CONDITIONS                    | MIN.            | MAX.       | UNIT |  |

|------------------|-------------------------------|-------------------------------|-----------------|------------|------|--|

| $V_{DD}$         | supply voltage                | V <sub>SS</sub> = 0 V; note 1 | -1.8            | +6         | V    |  |

| V <sub>I</sub>   | all input voltages            |                               | V <sub>SS</sub> | $V_{DD}$   | ٧    |  |

|                  | output short-circuit duration |                               |                 | indefinite |      |  |

| T <sub>amb</sub> | operating ambient temperature |                               | -10             | +60        | °C   |  |

| T <sub>stg</sub> | storage temperature           |                               | -30             | +100       | °C   |  |

## Note

1. Connecting the battery with reversed polarity does not destroy the circuit, but in this condition a large current flows, which will rapidly discharge the battery.

## **HANDLING**

Inputs and outputs are protected against electrostatic discharges in normal handling. However, to be totally safe, it is advisable to take handling precautions appropriate to handling MOS devices. Advice can be found in "Data Handbook IC16, General, Handling MOS Devices".

#### **CHARACTERISTICS**

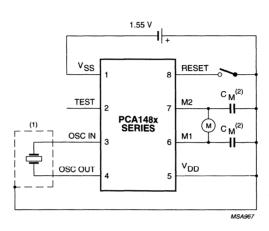

$V_{DD}$  = 1.55 V;  $V_{SS}$  = 0 V;  $f_{osc}$  = 32.768 kHz;  $T_{amb}$  = 25 °C; crystal:  $R_S$  = 20 k $\Omega$ ;  $C_1$  = 2 to 3 fF;  $C_L$  = 8 to 10 pF;  $C_0$  = 1 to 3 pF; unless otherwise specified.

Immunity against parasitic impedance = 20 M $\Omega$  between adjacent pins.

| SYMBOL             | PARAMETER                           | CONDITIONS                                                                          |      | TYP.     | MAX. | UNIT |

|--------------------|-------------------------------------|-------------------------------------------------------------------------------------|------|----------|------|------|

| Supply             |                                     |                                                                                     |      |          |      |      |

| V <sub>DD1</sub>   | supply voltage                      | T <sub>amb</sub> = -10 to +60 °C                                                    | 1.2  | 1.55     | 2.5  | V    |

| $\Delta V_{DD}$    | supply voltage variation            | transient within 1.2 V and 2.5 V                                                    | _    | <b>-</b> | 0.25 | V    |

| V <sub>DD2</sub>   | supply voltage                      | programming                                                                         | 5.0  | 5.1      | 5.2  | V    |

| $\Delta V_{DDP}$   | supply voltage pulse variation      | programming                                                                         | 0.55 | 0.6      | 0.65 | V    |

| I <sub>DD1</sub>   | supply current                      | between motor pulses                                                                | _    | 170      | 260  | nA   |

| I <sub>DD2</sub>   | supply current                      | V <sub>DD</sub> = 2.1 V                                                             | _    | 190      | 300  | nA   |

| I <sub>DD3</sub>   | supply current                      | stop mode; pin 8 connected to V <sub>DD</sub>                                       | _    | 180      | 280  | nA   |

| I <sub>DD4</sub>   | supply current                      | V <sub>DD</sub> = 2.1 V                                                             |      | 220      | 360  | nA   |

| I <sub>DD5</sub>   | supply current                      | T <sub>amb</sub> = -10 to +60 °C                                                    | _    | -        | 600  | nA   |

| Motor out          | put                                 |                                                                                     |      |          |      |      |

| V <sub>sat</sub>   | saturation voltage $\Sigma$ (P + N) | $R_{\rm M} = 2 \text{ k}\Omega; T_{\rm amb} = -10 \text{ to } +60 ^{\circ}\text{C}$ | -    | 150      | 200  | mV   |

| Z <sub>o(sc)</sub> | output short-circuit impedance      | between motor pulses<br>I <sub>transistor</sub> < 1 mA                              | _    | 200      | 300  | Ω    |

# PCA146x series

| SYMBOL              | PARAMETER               | CONDITIONS                       | MIN.     | TYP.                  | MAX.                 | UNIT |

|---------------------|-------------------------|----------------------------------|----------|-----------------------|----------------------|------|

| Oscillator          |                         |                                  |          |                       |                      |      |

| V <sub>OSC ST</sub> | starting voltage        |                                  | 1.2      | <u> </u>              | _                    | V    |

| g <sub>m</sub>      | transconductance        | V <sub>i(p-p)</sub> ≤ 50 mV      | 6        | 15                    | _                    | μS   |

| t <sub>osc</sub>    | start-up time           |                                  | -        | 1                     | -                    | s    |

| Δf/f                | frequency stability     | $\Delta V_{DD} = 100 \text{ mV}$ | T-       | $0.05 \times 10^{-6}$ | $0.3 \times 10^{-6}$ |      |

| C <sub>i</sub>      | input capacitance       |                                  | 8        | 10                    | 12                   | pF   |

| Co                  | output capacitance      |                                  | 12       | 15                    | 18                   | pF   |

| Voltage le          | vel detector            |                                  |          |                       |                      |      |

| $V_{LIT}$           | threshold voltage       |                                  | 1.62     | 1.80                  | 1.98                 | V    |

| V <sub>EOL</sub>    | threshold voltage       |                                  | 1.30     | 1.38                  | 1.46                 | V    |

| $\Delta V_{EOL}$    | hysteresis of threshold |                                  | _        | 10                    | -                    | mV   |

| TC <sub>EOL</sub>   | temperature coefficient |                                  | -        | -1                    | -                    | mV/K |

| Reset inp           | ut                      |                                  |          |                       |                      |      |

| fo                  | output frequency        |                                  | <u> </u> | 32                    | -                    | Hz   |

| $\Delta V_o$        | output voltage swing    | $R = 1 M\Omega; C = 10 pF$       | 1.4      | -                     | _                    | V    |

| t <sub>edge</sub>   | edge time               | $R = 1 M\Omega$ ; $C = 10 pF$    | -        | 1                     |                      | μs   |

| l <sub>im</sub>     | peak input current      | note 1                           | _        | 320                   | -                    | nA   |

| I <sub>i(av)</sub>  | average input current   |                                  | -        | 10                    | -                    | nA   |

# Note

1. Duty factor is 1 : 32 and RESET =  $V_{DD}$  or  $V_{SS}$ .

# PCA146x series

# **TIMING PARAMETERS**

| SYMBOL            | PARAMETER                                    | SECTION                       | VALUE                  | OPTION          | UNIT |

|-------------------|----------------------------------------------|-------------------------------|------------------------|-----------------|------|

| t <sub>T</sub>    | cycle for motor pulse (note 1)               | motor pulse (Figs 2, 3 and 4) | 1                      | 5, 10, 12 or 20 | s    |

| t <sub>P</sub>    | motor pulse width                            |                               | 7.81                   | 3.9 or 5.9      | ms   |

| t <sub>DF</sub>   | duty factor                                  |                               | 977                    | _               | μs   |

| t <sub>ONL</sub>  | last duty factor on                          |                               | 61 to 305              | _               | μs   |

| t <sub>v</sub>    | voltage detection cycle                      | level mode                    | 60                     | _               | s    |

| t <sub>SON</sub>  | duty factor on                               | silver-oxide mode (Fig.3)     | 550 to 794             | _               | μs   |

| t <sub>SOFF</sub> | duty factor off                              |                               | 427 to 183             | _               | μs   |

| t <sub>SONF</sub> | first duty factor on                         |                               | 488                    | _               | μs   |

| t <sub>AOFF</sub> | additional duty factor off                   | lithium mode (Fig.4)          | 183                    | -               | μs   |

| t <sub>LON</sub>  | duty factor on                               |                               | 305 to 611             | -               | μs   |

| t <sub>LOFF</sub> | duty factor off                              |                               | 672 to 366             | 1-              | μs   |

| t <sub>LONF</sub> | first duty factor on                         |                               | 244                    | _               | μs   |

| t <sub>E</sub>    | EOL sequence                                 | end-of-life mode              | 4                      | 1-              | s    |

| t <sub>E1</sub>   | motor pulse width                            |                               | tp                     | _               | ms   |

| t <sub>E2</sub>   | time between pulses                          |                               | 31.25                  | _               | ms   |

| t <sub>D</sub>    | detection sequence                           | detection (Fig.7)             | 4.3 to 28.3            | 1-              | ms   |

| t <sub>DS</sub>   | short-circuited motor                        |                               | 977                    | _               | μs   |

| t <sub>DI</sub>   | dissipation of energy                        |                               | 977                    | -               | μs   |

| t <sub>MC</sub>   | measurement cycle                            |                               | 488                    | _               | μs   |

| t <sub>M1</sub>   | phase 1                                      |                               | 244                    | _               | μs   |

| t <sub>M2</sub>   | phase 2 (measure window)                     |                               | 61                     | _               | μs   |

| t <sub>M3</sub>   | phase 3                                      |                               | 122                    |                 | μs   |

| t <sub>M4</sub>   | phase 4                                      |                               | 61                     | _               | μs   |

| Р                 | positive current polarities                  |                               | 1                      | P < N           |      |

| N                 | negative current polarities                  |                               | 2                      | 2 to 6          |      |

| t <sub>C</sub>    | correction sequence                          | correction sequence (Fig.8)   | t <sub>P</sub> + 30.27 | _               | ms   |

| t <sub>C1</sub>   | small pulse width                            |                               | 977                    | _               | μs   |

| t <sub>C2</sub>   | large pulse width                            |                               | tp                     | _               | ms   |

|                   | cycles for motor-pulses in:                  | testing                       |                        |                 |      |

| t <sub>T1</sub>   | test 1                                       |                               | 125                    | _               | ms   |

| t <sub>T2</sub>   | test 2                                       |                               | 31.25                  | _               | ms   |

| t <sub>T3</sub>   | test 3                                       | Fig.10                        | 31.25 to 39            | _               | ms   |

| t <sub>DEB</sub>  | debounce time for<br>RESET = V <sub>DD</sub> |                               | 14.7 to 123.2          | _               | ms   |

# Note

1. No option available when EOL indication is required.

# PCA146x series

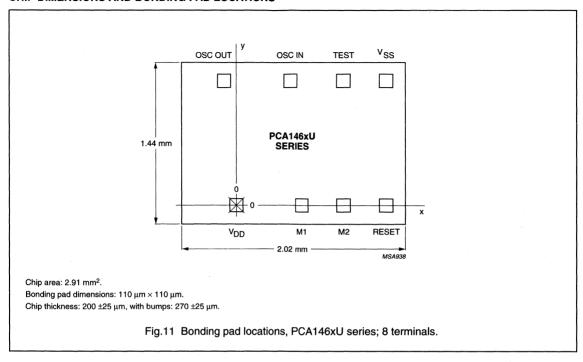

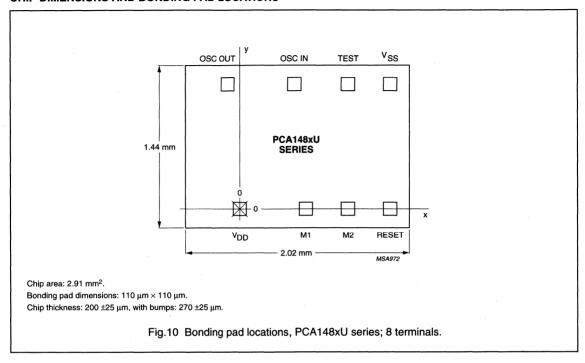

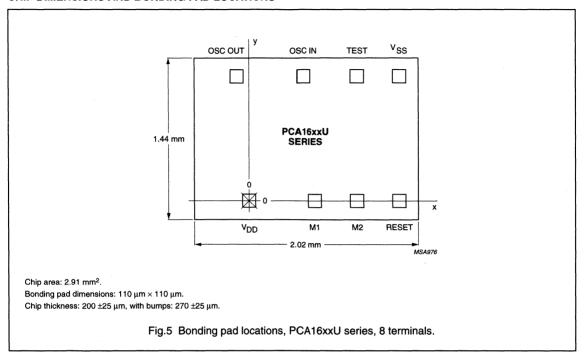

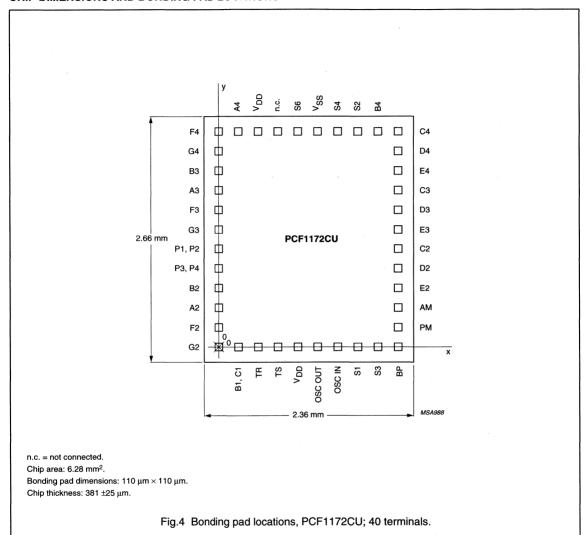

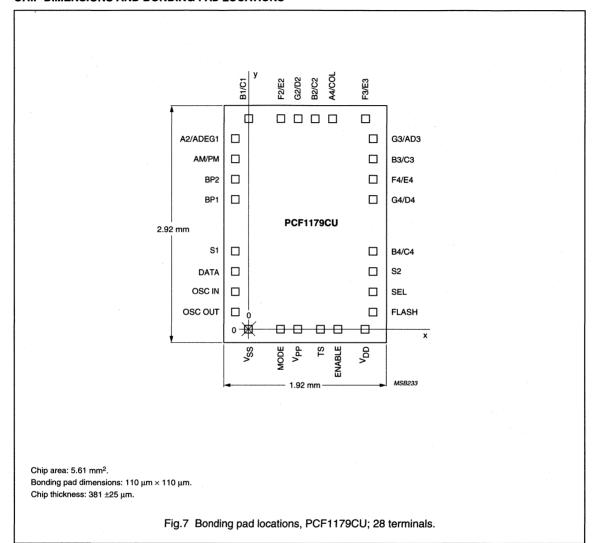

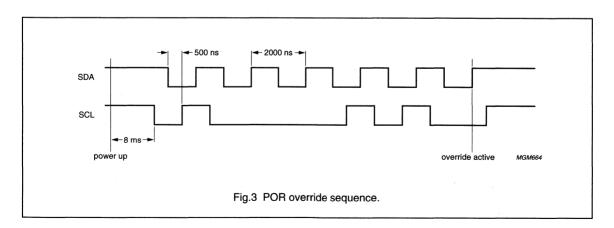

## CHIP DIMENSIONS AND BONDING PAD LOCATIONS